���荞�݃v���O���~���O

�@�g�W�v���O�����̍\���Ő��������悤�ɁA�SE�����̃v���O�����ł͖w�ǂ̏��������荞�ݏ����ōs���B���荞�ݏ����̌��ʂ̓O���[�o���ϐ��ɔ��f�����B���������i�j�v���O�����͊��荞�݂ɑ��鏉���ݒ�A�O���[�o���ϐ����Q�Ƃ��Ẵ��[�v�����������s���Ă���B

���荞�ݏ������w�ǂ̏����������Ȃ��B

�����ł͊��荞�ݏ����v���O�����ɂ��Đ�������B

�Ȃ��A�g�d�v���g�p����ƁA�������������D���Ƃ����t�@�C���������쐬����A���ׂĂ̊��荞�ݏ��������̃t�@�C�����ɋL�q����悤�ɂȂ�B�������x�N�^�[�ԍ��O�̊��荞�݁i���Z�b�g���荞�݁j�͓���ł��邽�߁Aresetprg.c�Ƃ����t�@�C���Ƃ��č쐬�����B

�P�D�@���荞�݂Ƃ�

�@���s���̏������A���荞�݃C�x���g�i��O�����v���j�ɂ���Ē��f���A���荞�ݏ����v���O���������s���A���̏������I���������ƂŁA�O�̏������ĊJ����@�\�B

�Q�D�@���荞�݂̎��

�Q�D�P�@�}�X�N�\���ǂ����ŕ���

| ��� |

|

| NMI |

Non-Maskable-Interrupt. �}�X�N�s�\�Ȋ��荞�݁B

�b�b�q�̂h�r�b�g���P�ł����荞�݂���������B

�ł��D��x���������荞�݂ŁA�f�[�^���o�͂ɂ͎g�p���ꂸ�A��d���o�ȂǂɎg�p����B |

| NON-NMI |

�}�X�N�\�Ȋ��荞�݁i�b�b�q�̂h�r�b�g�Ŋ��荞�݂��}�X�N�ł��銄�荞�݁j�B

�b�b�q�̂h�r�b�g���h�P�h�Ƃ���Ɗ��荞�݂������Ȃ��A�h�O�h�Ƃ���Ɗ��荞�݂���������B |

�Q�D�Q�@���荞�݂̎�ށE�x�N�^�e�[�u��

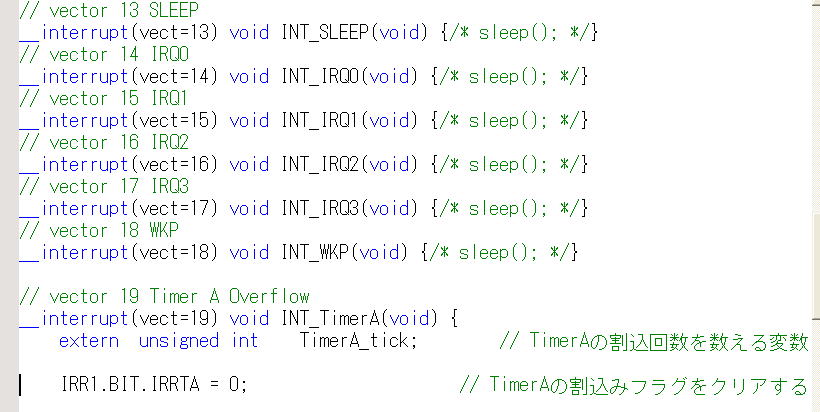

�@���荞�݂́A���\�̂悤�ɔ������i�v�����j�ŕ��ނ����B�܂����荞�ݗD�揇�ʂ́A���̕\�̏��ԂɂȂ��Ă���B���Z�b�g�[�q����̊��荞�ݗD�揇�ʂ���ԍ����B

���荞�ݗv���Ɗ��荞�ݏ������̑Ή����e�[�u���ɂ������̂�

�u���荞�݃e�[�u���v�ł���A�e�[�u���ł̏��Ԃ��u�x�N�g���ԍ��v�ł���B�g�W�̊��荞�ݗD�揇�ʂ́A���܂��܃x�N�g���ԍ��̏��ԂɂȂ��Ă���B

�x�N�^�e�[�u���ɂ͏������ւ̃A�h���X���S�o�C�g�ŋL������Ă���B���荞�݂���������Ƃ��̃A�h���X���o�b�ɃZ�b�g����Ċ��荞�ݏ����������s�����B

| ������ |

��O�����v�� |

�x�N�g���ԍ� |

| ���Z�b�g�[�q |

���Z�b�g |

�O |

|

�V�X�e���\�� |

�P�`�U |

| �O�������ݒ[�q |

NMI |

�V |

| CPU |

�g���b�v���߁@���O |

�W |

| �g���b�v���߁@���P |

�X |

| �g���b�v���߁@���Q |

�P�O |

| �g���b�v���߁@���R |

�P�P |

| �A�h���X��u���[�N |

�u���[�N�������� |

�P�Q |

| CPU |

�X���[�v���߂̎��s�ɂ�钼�ڑJ�� |

�P�R |

| �O�������ݒ[�q |

IRQ0 |

�P�S |

| IRQ1 |

�P�T |

| IRQ2 |

�P�U |

| IRQ3 |

�P�V |

| WKP(�E�G�C�N�A�b�v�j |

�P�W |

| �^�C�}�[A |

�I�[�o�[�t���[ |

�P�X |

|

�V�X�e���\�� |

�Q�O |

| �^�C�}�[W |

�C���v�b�g�E�L���v�`��A/�R���y�A�E�}�b�`A |

�Q�P |

| �C���v�b�g�E�L���v�`��B/�R���y�A�E�}�b�`B |

| �C���v�b�g�E�L���v�`��C/�R���y�A�E�}�b�`C |

| �C���v�b�g�E�L���v�`��D/�R���y�A�E�}�b�`D |

| �I�[�o�[�t���[ |

| �^�C�}�[V |

�R���y�A�E�}�b�`A |

�Q�Q |

| �R���y�A�E�}�b�`B |

| �I�[�o�[�t���[ |

| SCI3 |

��M�f�[�^�t�� |

�Q�R |

| ���M�f�[�^�G���v�e�C |

| ���M�I�� |

| ��M�G���[ |

| IIC2 |

���M�f�[�^�G���v�e�C�A���M�I�� |

�Q�S |

| ��M�f�[�^�t�� |

| �A�[�r�g���[�V�������X�g/�I�[�o�[�����G���[ |

| NACK���o�A��~�������o |

| AD�R���o�[�^ |

AD�ϊ��I�� |

�Q�T |

�R�D�@CPU�̊��荞�ݓ���

�R�D�P�@���荞�݂̊J�n

�@���荞�݂ƂȂ�C�x���g�����������Ƃ��A�b�o�t�͈ȉ��̓�����s���B

�@���̔������ł̊��荞�݂��A������Ă��邩�`�F�b�N�B

���Ӌ@�튄�荞�݂ł́A�v���ɑΉ��������荞���r�b�g�Ɗ��荞�݃t���O���h�P�f�ł��邱�ƁB

�ACCR�̊��荞�݃}�X�N�r�b�g�iI�r�b�g�j���f�O�h�ł���i���荞�݂�������Ă���j���`�F�b�N�B

�@�@�i���jNMI���荞�݂ł͂��̃`�F�b�N�͖����B

�@�ȏ�̃`�F�b�N���p�X�����Ƃ��A���荞�݂���������B

�BPC�̒l��CCR�̒l���X�^�b�N�ɑޔ�����B

�CCCR�̊��荞�݃}�X�N�r�b�g�iI�r�b�g�j���Z�b�g�B

�@�@�b�o�t�́A���荞�݂����s���́A���d�̊��荞�݂��t���Ȃ��悤�ɂ��Ă���B

�D�x�N�g���A�h���X��PC�̒l�ɃZ�b�g���āA���荞�݃v���O���������s�B

�i���m�ɂ́A�x�N�g���A�h���X�R�Q�r�b�g��ǂ݁A���ʂ̂Q�O�r�b�g���A�h���X�Ƃ��Ďg�p����o�b�ɃZ�b�g�����j�B

�R�D�Q�@���荞�ݏ���

�@���荞�ݏ����v���O���������s�����B

�@���̃v���O�����́A�I������Ƃ��ARTE���߁i�A�b�Z���u����RTE���߁j�s����B

�@

�R�D�R�@���荞�݂̏I��

�@�b�o�t���q�s�d���߂���M�����Ƃ��A�ȉ��̓�����s���B

�@�X�^�b�N�ɑޔ����Ă���PC�̒l�ACCR�̒l��

�A���̏������ĊJ����B

����Ŋ��荞�ݏ����͏I�����āA���̃v���O�����ɕ��A����B

�i���Ӂj��L�̓���R�D�P�ƂR�D�Q�́A�v���O�����ł͂Ȃ��A�b�o�t�{�̋@�\�̓���Ƃ��Ď��s�����B

�S�D�@���荞�݂ɑΉ�����v���O����

�@�Q�̕����i���荞�݂ɑ��鏀���E��t�ݒ�A���荞�݂ɑ��鉞���j����\�������B

�S�D�P�@���荞�݂ɑ��鏀���E��t�ݒ�

�i�P�j�x�N�^�[�e�[�u���̊m��

�@�@�g���W�}�C�R���ł͂g�f�O�O�O�O����g�f�O�O�R�R�܂ł̓x�N�^�[�e�[�u���Ă���Ƃ��Ďn�߂���m�ۂ���Ă���B

�i�Q�j���荞�ݏ������̒�`

�@�@���荞�݃e�[�u���ɁA���荞�ݏ������ւ̃A�h���X�ƋL�����A���荞�ݏ������̎��̂��`����B

�@�@�g�d�v�ł͈ȉ��̂悤�ɋL�q����B

#pragma interrupt irq0(vect=12)

void irq0(void); |

#pragma�͂b�R���p�C���ւ̎w����������́B�������O�Ƃ����������荞�݊��ł��邱�Ƃ������Bvect=12�́A���ꂪ���荞�݃x�N�g���P�Q�ł��邱�Ƃ������B

void irq0(void);�́A���荞�ݏ������̃v���g���C�v�錾 |

| void irq0(void){ } |

���荞�ݏ������{�̂̋L�q�B |

�@���荞�ݏ������́A���荞�݂����������Ƃ��ɏ���������B

����͂��������^�̊��ł��胊�^�[���l�͖����B

�@���������i�j�v���O�����Ƃ͕ʂɋL�q����B

�@���������ăt���[�`���[�g�ł́A�Ɨ��������͂Əo�͂��������`���[�g�ɂȂ�B

�i�R�j�x�N�^�[�e�[�u���ւ̊��荞�ݏ������A�h���X�̓o�^

�@��L�̃\�[�X�R�[�h���R���p�C���A�����N����ƁA�����N�̂Ƃ��ɃA�h���X���e�[�u���ɓo�^�����B

�@

�i�S�j���荞�ݎ�t�ݒ�

�@����͂��������i�j�v���O�����A�܂����荞�ݏ����v���O�����������̊��荞�݂��t���邽�߂ɐݒ肷��B

�@�@�@�@�@�b�b�q�̂h�r�b�g���Z�b�g�i���荞�֎~���[�h�j����B

�@�@�@�@�@�@�@����́A�ȉ��̇A�̐ݒ肪�A���荞�֎~���[�h�ł����Ȃ��K�v�����邽�߂ł���B

�@�@�@�@�@�@�@�i���Ӂj

CCR�̃r�b�g�𑀍삷��ɂ́A���ʂȊ��@set_imask_ccr() ���g�p����B

�@�@�@�@�@�@�@�܂����̊����g�p����ɂ́A#include <machine.h> �Ƃ��āAmachine.h�t�@�C�����C���N���[�h����B

�@�@�@�@�A�������̊��荞�݂��t���邽�߂̊e��ݒ������B

�@�@�@�@�@�@�@�@���̐ݒ�́A���荞�ݔ������ɂ���āA�ݒ肷�郌�W�X�^���قȂ�B

�@�@�@�@�@�@�@�@�Ō�ɁA���荞�ݗv���ɑ��銄�荞�݃t���O���N���A����B

�@�@�@�@�@�@�@�@���̐ݒ�ڍׂ́A�T�D���荞�ݑΉ����W�X�^�@���Q�ƁB

�@�@�@�@�@�@�@�@

�@�@�@�@�B�b�b�q�̂h�r�b�g�����Z�b�g����i���荞�����[�h�j����B

�@HEW���g�p����ƁA��L�́i�P�j�A�i�Q�j�A�i�R�j�̓R�����g�t�R�[�h�Ŏ����쐬�����B

�@���������������̃R�����g���O�������ł悢�B�i�S�j�̕����͎��ۂɃv���O���~���O�i�R�[�f�C���O�j����K�v������B

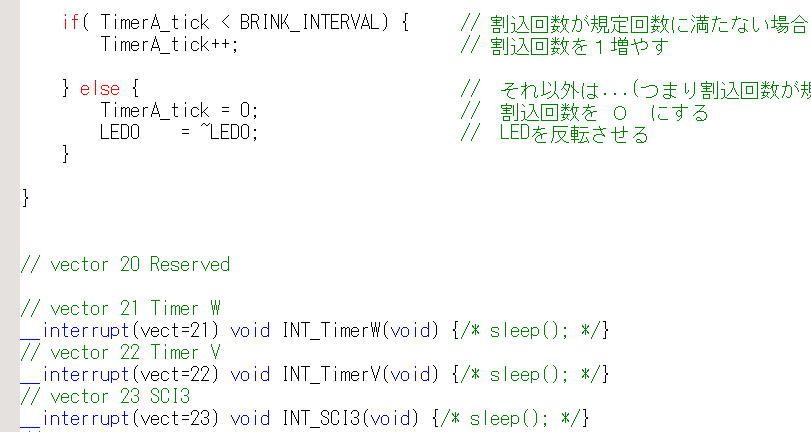

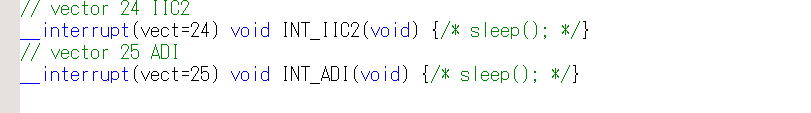

�S�D�Q�@���荞�݂ɑ��鉞��

���荞�ݏ������ɋL�q����B

�@�@�@�@�@�O����

�K�v�ɉ����āA�ėp���W�X�^��ޔ�����B

�@�@�@�@�A���荞�ݏ���

�B�㏈��

�@�@�@�@�@�@�@���荞�݃t���O���N���A����B

�@�@�@�@�@�@�@���荞�݃r�b�g���h�O�h�ɂ��Ċ��荞�݉\�Ƃ���

�@�@�@�@�@�@�@�@�@����Ŋ��荞�݂��Ăю�t������悤�ɂȂ�B

�@�@�@�@ �ėp���W�X�^�̕���������B

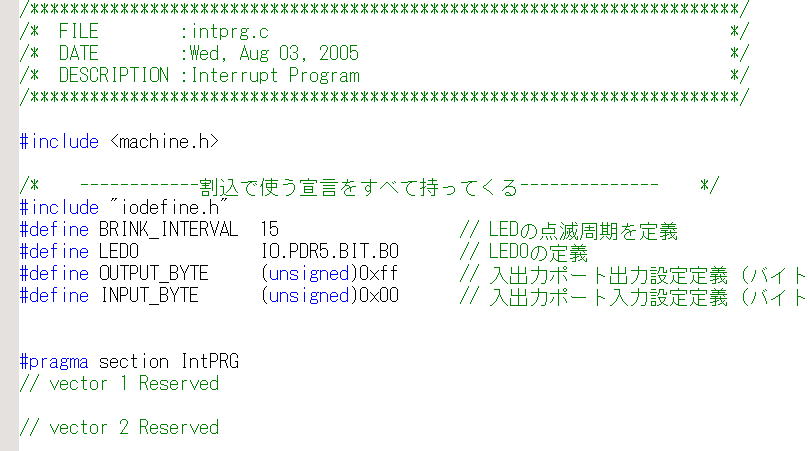

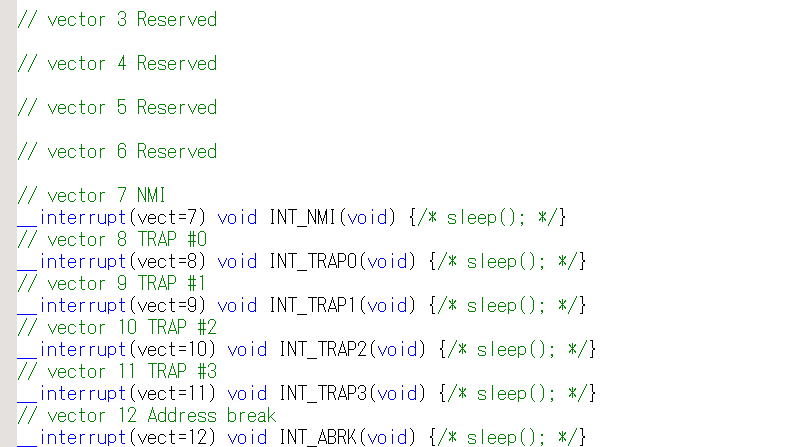

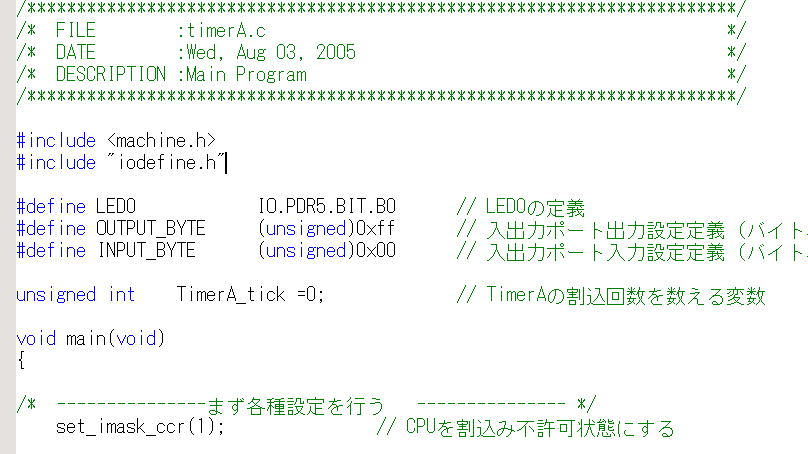

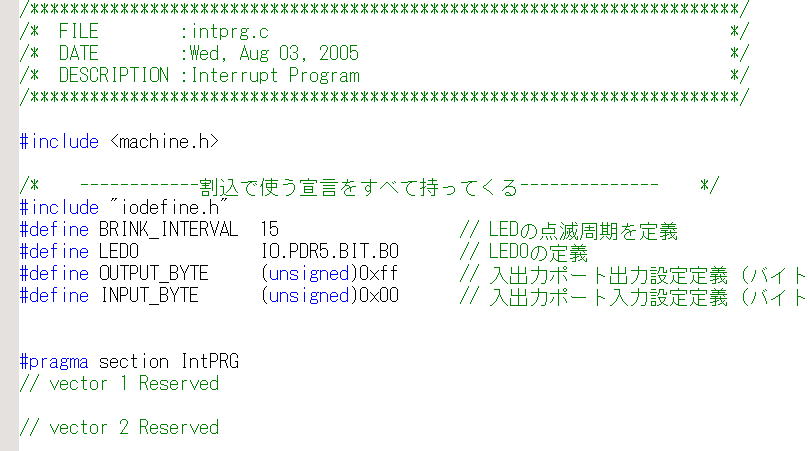

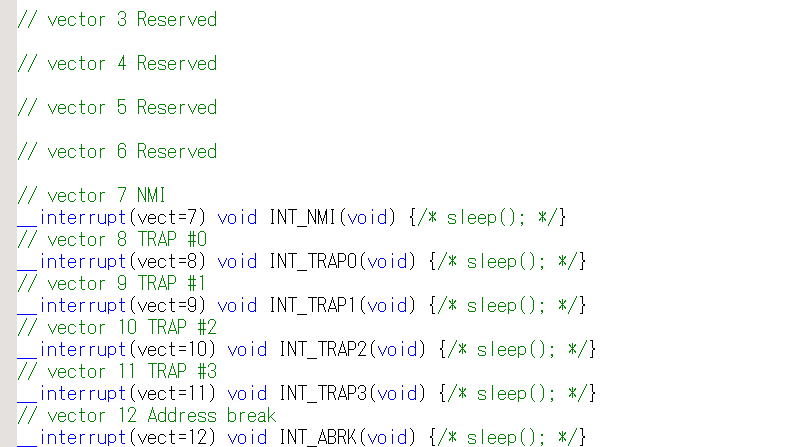

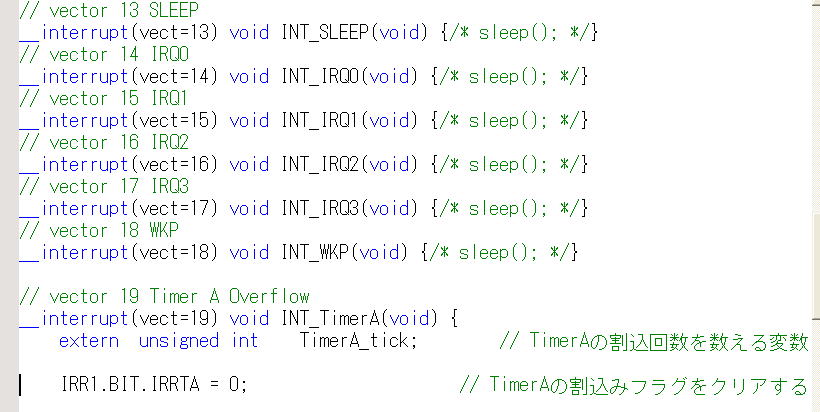

�g�d�v���g�p�����Ƃ��A���荞�݂Ɋւ���S�D�P�́i�P�j�A�i�Q�j�A�i�R�j�̊O�g�������쐬�����B�J���҂́A���������i�j���Ŋ��荞�ݎ�t�ݒ���L�q���Aintprog.c���Ŋ��荞�݂ɑ��������L�q���邾���ŁA���荞�݂��g�p���邱�Ƃ��ł���B

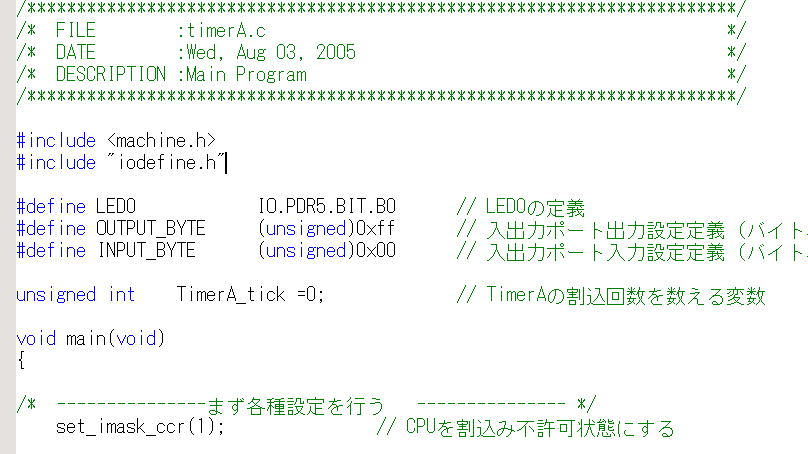

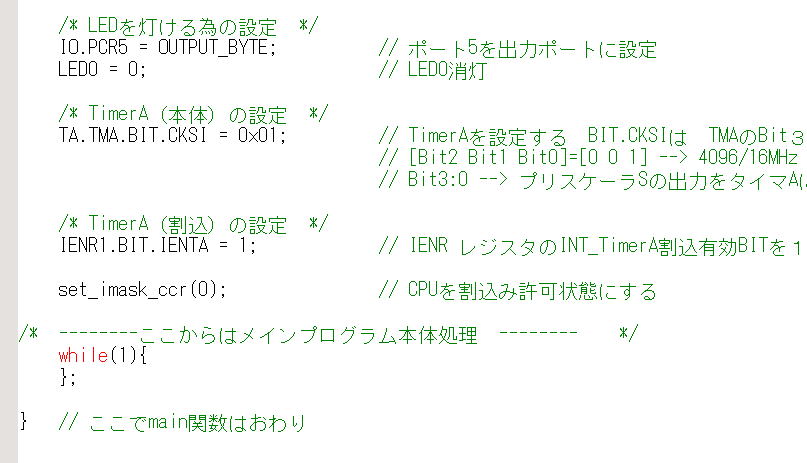

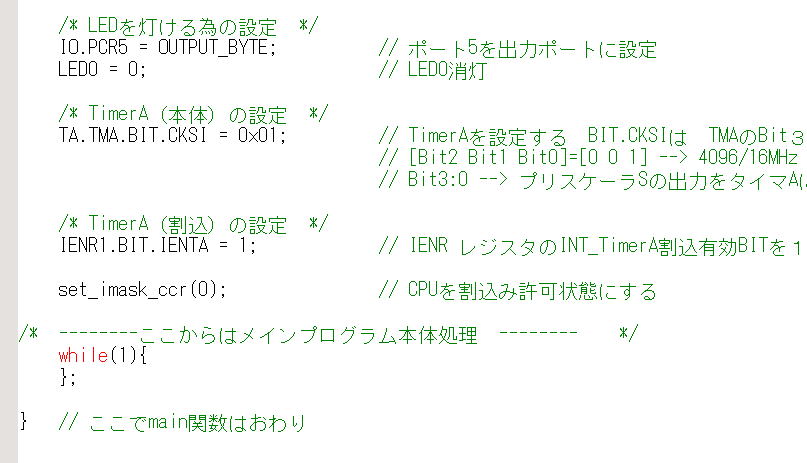

���������i�j���̗�

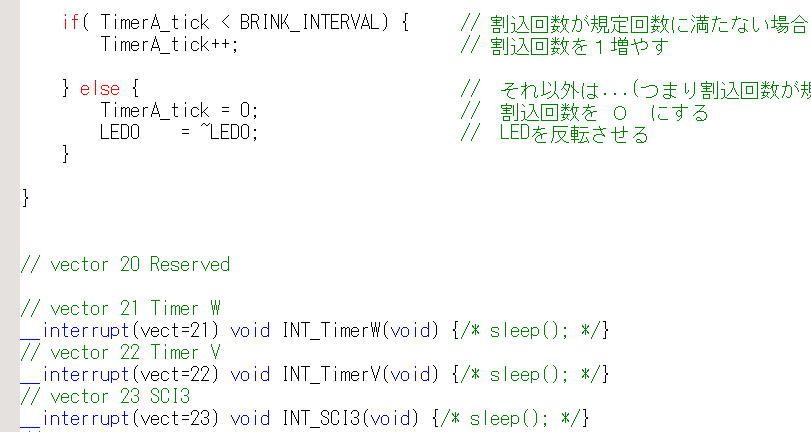

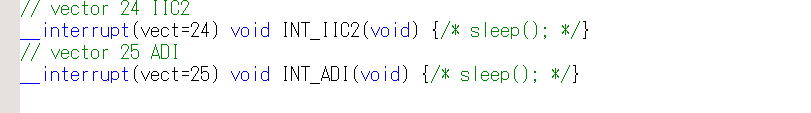

intprog.c�̗�

�T�D���荞�ݑΉ����W�X�^�y�уr�b�g

�T�D1�@IRQ�[�q���荞��

| ���W�X�^�ƃr�b�g |

���e |

�R���f�V�����R�[�h���W�X�^�i�b�b�q�j

�@�@���荞�݃}�X�N�r�b�g�i�h�j |

�S�̊��荞���ݒ�

���P�@���荞�ݗv�����}�X�N

���O�@���荞�ݗv���̃}�X�N�����i���荞�݉\�j |

�|�[�g�P�E�|�[�g���[�h���W�X�^�i�o�l�q�P�j

�@�@�o�P�S/�h�q�p�O�@�\�I���r�b�g�i�h�q�p�O�j

�@�@�o�P�T/�h�q�p�P�@�\�I���r�b�g�i�h�q�p�P�j

�@�@�o�P�U/�h�q�p�Q�@�\�I���r�b�g�i�h�q�p�Q�j

�@�@�o�P�V/�h�q�p�R�@�\�I���r�b�g�i�h�q�p�R�j |

�[�q�����荞�ݒ[�q�Ƃ��Đݒ肷�邩�A�ėp���o�̓|�[�g�Ƃ��邩�A�|�[�g�̋@�\�I�����郌�W�X�^

���O�@�ėp���o�̓|�[�g

���P�@IRQ�O�C�P�C�Q�C�R���荞�ݓ��͒[�q |

���荞�݃G�b�W�Z���N�g���W�X�^�i�h�d�f�q�P�j

�@�@�h�q�p�O�G�b�W�Z���N�g�r�b�g�i�h�d�f�O�j

�@�@�h�q�p�P�G�b�W�Z���N�g�r�b�g�i�h�d�f�P�j

�@�@�h�q�p�Q�G�b�W�Z���N�g�r�b�g�i�h�d�f�Q�j

�@�@�h�q�p�R�G�b�W�Z���N�g�r�b�g�i�h�d�f�R�j�@ |

���荞�ݐM���̗����オ��A������̎w��

���O�@������G�b�W���o

���P�@�����オ��G�b�W���o

|

���荞�݃C�l�[�u�����W�X�^�i�h�d�m�q�P�j

�@�@�h�q�p�O�����v���C�l�[�u���r�b�g�i�h�d�m�O�j

�@�@�h�q�p�P�����v���C�l�[�u���r�b�g�i�h�d�m�P�j

�@�@�h�q�p�Q�����v���C�l�[�u���r�b�g�i�h�d�m�Q�j

�@�@�h�q�p�R�����v���C�l�[�u���r�b�g�i�h�d�m�R�j |

�O���[�q�����荞�݉\�ݒ�

���P�@���荞�ݗv���C�l�[�u��

���O�@�f�Z�[�u�� |

���荞�݃t���O���W�X�^�i�h�q�q�P�j

�@�@�h�q�p�O�����ݗv���t���O�r�b�g�i�h�q�q�h�O�j

�@�@�h�q�p�P�����ݗv���t���O�r�b�g�i�h�q�q�h�P�j

�@�@�h�q�p�Q�����ݗv���t���O�r�b�g�i�h�q�q�h�Q�j

�@�@�h�q�p�R�����ݗv���t���O�r�b�g�i�h�q�q�h�R�j |

�O���[�q���荞�݃t���O

�Z�b�g�����F�@IRQ0�`�R�[�q�����荞�ݓ��͂Ɏw�肳��A�w��̃G�b�W�����o�����Ƃ��B

�N���A�����F�@�f�O�f���������Ƃ��B

|

�T�D�Q�@�m�l�h�[�q���荞��

| ���W�X�^�ƃr�b�g |

���e |

���荞�݃G�b�W�Z���N�g���W�X�^�i�h�d�f�q�P�j

�@�@NMI�G�b�W�Z���N�g�r�b�g�iNMIEG�j�@�@�@ |

���荞�ݐM���̗����オ��A������̎w��

���O�@������G�b�W���o

���P�@�����オ��G�b�W���o

|

�T�D�R�@�s���������`���荞��

TimerA�͂W�r�b�g�̃J�E���^�ŃI�[�o�t���[�����Ƃ��i�Q�T�T����O�ɕω������Ƃ��j���荞�݂���������B

| ���W�X�^�ƃr�b�g |

���e |

�R���f�V�����R�[�h���W�X�^�i�b�b�q�j

�@�@���荞�݃}�X�N�r�b�g�i�h�j |

�S�̊��荞���ݒ�

���P�@���荞�ݗv�����}�X�N

���O�@���荞�ݗv���̃}�X�N�����i���荞�݉\�j |

| �v���X�P�[���i�o�r�r�j |

�V�X�e���N���b�N����͂Ƃ���P�R�r�b�g�J�E���^�B���̓N���b�N�ݒ� |

�^�C�}���[�h���W�X�^�i�s�l�`�j

�@�@�C���^�[�i���N���b�N�Z���N�ƃr�b�g�O

�@�@�i�s�l�`�O�j

�@�@�C���^�[�i���N���b�N�Z���N�g�r�b�g�P

�@�@�i�s�l�`�P�j

�@�@�C���^�[�i���N���b�N�Z���N�g�r�b�g�Q

�@�@�i�s�l�`�Q�j

�@�@�C���^�[�i���N���b�N�Z���N�g�r�b�g�R

�@�@�i�s�l�`�R�j�@ |

�v���X�P�[���̑I���A���̓N���b�N�̑I��

���̕\���Q�ƁB |

�C�}���[�h���W�X�^�i�s�l�`�j

�@�@�@�C���^�[�i���N���b�N�Z���N�g�r�b�g�R

�@�@�@�i�s�l�`�R�j |

�^�C�}A�̓��샂�[�h�I��

���O�@�v���X�P�[��S

���@�v���X�P�[��W |

���荞�݃C�l�[�u�����W�X�^�i�h�d�m�q�P�j

�@�@�^�C�}�`���荞�݃C�l�[�u���r�b�g

�@�@�i�h�d�m�s�`�j |

�^�C�}���荞���ݒ�

���P�@�^�C�}A�I�[�o�t���[���荞�݃C�l�[�u��

���O�@�f�Z�[�u�� |

���荞�݃t���O���W�X�^�i�h�q�q�P�j

�@�@�^�C�}�`���荞�ݗv���t���O�r�b�g

�@�@�i�h�q�q�s�`�j |

���荞�݃t���O

�Z�b�g�����F�@IRQ0�`�R�[�q�����荞�ݓ��͂Ɏw�肳��A�w��̃G�b�W�����o�����Ƃ��B

�N���A�����F�@�f�O�f���������Ƃ��B |

| �^�C�}�J�E���^�i�s�b�`�j |

�W�r�b�g�^�C�}�J�E���^�A���荞�ݎ����̐ݒ� |

���̓N���b�N�̑I��

���̓V�X�e���N���b�N�B�R�U�U�SF�ł͂P�UMH���B

| �����فE�N���b�N�Z���N�g�r�b�gTCA |

TCA���̓N���b�N�̑I�� |

| TMA3 |

TMA2 |

TMA1 |

TMA0 |

| �O |

�O |

�O |

�O |

��/�W�P�X�Q���J�E���g |

| �O |

�O |

�O |

�P |

��/�S�O�X�U���J�E���g |

| �O |

�O |

�P |

�O |

��/�Q�O�S�W���J�E���g |

| �O |

�O |

�P |

�P |

��/�T�P�Q���J�E���g |

| �O |

�P |

�O |

�O |

��/�Q�T�U���J�E���g |

| �O |

�P |

�O |

�P |

��/�P�Q�W���J�E���g |

| �O |

�P |

�P |

�O |

��/�R�Q���J�E���g |

| �O |

�P |

�P |

�P |

��/�W���J�E���g |

�T�D�S�@�s���������v���荞��

TimerW�͂P�U�r�b�g�̃J�E���^�ŁA�I�[�o�t���[�����Ƃ��A�R���y�A�}�b�`�����Ƃ��A���荞�݂���������B

| ���W�X�^�ƃr�b�g |

���e |

�R���f�V�����R�[�h���W�X�^�i�b�b�q�j

�@�@���荞�݃}�X�N�r�b�g�i�h�j |

�S�̊��荞���ݒ�

���P�@���荞�ݗv�����}�X�N

���O�@���荞�ݗv���̃}�X�N�����i���荞�݉\�j |

�^�C�}���[�h���W�X�^W�i�s�l�q�v�j

�@�@�J�E���^�X�^�[�g�r�b�g�i�b�s�r�j�@�@ |

�J�E���^�X�^�[�g�w��

���O�@TCNT�J�E���^�����~

���P�@TCNT�J�E���^������{ |

�^�C�}���[�h���W�X�^W�i�s�l�q�v�j

�@�@�o�v�l���[�h�a�r�b�g�i�o�v�l�a�j

�@�@�@�@FTIOB�[�q

�@�@�o�v�l���[�h�b�r�b�g�i�o�v�l�b�j

�@�@�@�@FTIOC�[�q

�@�@�o�v�l���[�h�c�r�b�g�i�o�v�l�c�j

�@�@�@�@FTIOD�[�q |

�^�C�}�̏o�̓��[�h�I��

���O�@�ʏ�̃A�E�g�v�b�g�E�R���y�A�o��

���P�@PWM�o�� |

�^�C�}���[�h���W�X�^W�i�s�l�q�v�j

�@�@�N���b�N�Z���N�g�O�r�b�g�iCKS0)

�@�@�N���b�N�Z���N�g�P�r�b�g�iCKS�P)

�@�@�N���b�N�Z���N�g�Q�r�b�g�iCKS�Q) |

TCNT�̓��̓N���b�N�ݒ�i�v���X�P�[���j

���̕\���Q�ƁB |

�^�C�}�R���g���[�����W�X�^�i�s�b�q�v�j

�@�@�^�C�}�o�̓��x���E�Z�b�g�`�r�b�g�i�s�n�`�j

�@�@�@�@FTIOA�[�q

�@�@�^�C�}�o�̓��x���E�Z�b�g�a�r�b�g�i�s�n�a�j

�@�@�@�@FTIOB�[�q

�@�@�^�C�}�o�̓��x���E�Z�b�g�b�r�b�g�i�s�n�b�j

�@�@�@�@FTIOC�[�q

�@�@�^�C�}�o�̓��x���E�Z�b�g�c�r�b�g�i�s�n�c�j

�@�@�@�@FTIOB�[�q |

�R���y�A�}�b�`�O�̏o�͒l�I��

���O�@�o�͒l�O

���P�@�o�͒l�P

|

| �^�C�}�J�E���^�i�s�b�m�s�j |

�P�U�r�b�g�J�E���^ |

| �W�F�l�������W�X�^�`�i�f�q�`�j |

�o�v�l�o�͂̎����ݒ� |

| �W�F�l�������W�X�^�a�i�f�q�a�j |

�e�s�h�n�a�[�q�o�v�l�g�`�̂g�������߂� |

| �W�F�l�������W�X�^�b�i�f�q�b�j |

�e�s�h�n�b�[�q�o�v�l�g�`�̂g�������߂� |

| �W�F�l�������W�X�^�c�i�f�q�c�j |

�e�s�h�n�c�[�q�o�v�l�g�`�̂g�������߂� |

�^�C�}�C���^���v�g�C�l�[�u�����W�X�^W

�@�@�i�s�h�d�q�v�j

�@�@�C�l�[�u���`�r�b�g�i�h�l�h�d�`�j

�@�@�C�l�[�u���a�r�b�g�i�h�l�h�d�a�j

�@�@�C�l�[�u���b�r�b�g�i�h�l�h�d�b�j

�@�@�C�l�[�u���c�r�b�g�i�h�l�h�d�c�j

�@�@�I�[�o�t���[�C�l�[�u���r�b�g�i�n�u�h�d�j |

�R���y�A�}�b�`���荞�݃C�l�[�u���ݒ�

���P�@���荞�݃C�l�[�u��

��0�@�f�Z�[�u�� |

�^�C�}�X�e�[�^�X���W�X�^W�i�s�r�q�v�j

�@�@�t���O�`�i�h�l�e�`�j

�@�@�t���O�a�i�h�l�e�a�j

�@�@�t���O�b�i�h�l�e�b�j

�@�@�t���O�c�i�h�l�e�c�j

�@�@�I�[�o�t���[�t���O�i�n�u�e�j |

���荞�݃t���O

�Z�b�g�����F�@IGRDA�`GRD���A�E�g�v�b�g�R���y�A���W�X�^�Ƃ��ċ@�\���ATCNT�ƈ�v�����Ƃ��B

�N���A�����F�@�f�O�f���������Ƃ�

|

�^�C�}�X�e�[�^�X���W�X�^W�i�s�r�q�v�j

�@�@�@�I�[�o�t���[�t���O�i�n�u�e�j |

�^�C�}�[�I�[�o�[�t���[���荞�݃t���O

�Z�b�g�����F�@TCNT��H'FFFF����H'0000�I�[�o�t���[�����Ƃ��B

�N���A�����F�@�f�O�f���������Ƃ� |

�N���b�N�Z���N�g�r�b�g�iCKS)�ƃ^�C�}�J�E���^�iTCNT)�̓��̓N���b�N�I��

| �N���b�N�Z���N�g�r�b�g |

TCNT���̓N���b�N�̑I�� |

| CKS2 |

CKS1 |

CKS1 |

�N���b�N�� |

���e |

| �O |

�O |

�O |

�����N���b�N |

�����J�E���g |

| �O |

�O |

�P |

��/�Q���J�E���g |

| �O |

�P |

�O |

��/�S���J�E���g |

| �O |

�P |

�P |

��/�W���J�E���g |

| �P |

��

�i�C�Ӂj |

��

�i�C�Ӂj |

�O���C�x���g

�iFTCI) |

�����オ��G�b�W���J�E���g |

�T�D�T�@�`�c�ϊ��I�����荞��

AD�ϊ����I�������Ƃ����荞�݂���������B

| ���W�X�^�ƃr�b�g |

���e |

�R���f�V�����R�[�h���W�X�^�i�b�b�q�j

�@�@���荞�݃}�X�N�r�b�g�i�h�j |

�S�̊��荞���ݒ�

���P�@���荞�ݗv�����}�X�N

���O�@���荞�ݗv���̃}�X�N�����i���荞�݉\�j |

A�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�`�c�G���h�t���O�r�b�g�i�`�c�e�j�@ |

�`�c�G���h�t���O

�Z�b�g�����F�@AD�ϊ��I���̂Ƃ�

�N���A�����F�@�f�O�f���������Ƃ�

|

�`�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�`�c�C���^�v�g�C�l�[�u���r�b�g�i�`�c�h�d�j�@ |

�`�c�ϊ��I�����荞�݉\�ݒ�A

���O�@�֎~

���P�@���� |

�`�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�`�c�X�^�[�g�t���O�r�b�g�i�`�c�r�s�j |

AD�ϊ��X�^�[

���O�@��~

���P�@�J�n�g |

�`�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�X�L�������[�h�r�b�g�i�`�c�r�j |

�X�L�������[�h

���O�@�P�ꃂ�[�h

���P�@�X�L�������[�h |

�`�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�N���b�N�Z���N�g�r�b�g�iCKS) |

AD�ϊ����Ԃ̐ݒ�

���O�@�P�R�S�X�e�[�g

���P�@�V�O�X�e�[�g |

�`�c�R���g���[��/�X�e�[�^�X���W�X�^

�i�`�c�b�r�q�j

�@�@�`�����l���Z���N�g�O�r�b�g�iCH0)

�@�@�`�����l���Z���N�g�P�r�b�g�iCH�P)

�@�@�`�����l���Z���N�g�Q�r�b�g�iCH�Q) |

�A�i���O���̓`�����l���̐ݒ�

���̕\���Q�ƁB |

�`�c�R���g���[�����W�X�^�i�`�c�b�q�j

�@�@�g���K�[�C�l�[�u���i�s�q�f�d�j |

�O���g���K�\���ǂ����̐ݒ�

���O�@�֎~

���P�@���� |

| �`�c�f�[�^���W�X�^�`�i�`�c�c�q�`�j |

�P�O�r�b�g�̂`�c�ϊ��f�[�^���i�[ |

| �`�c�f�[�^���W�X�^�a�i�`�c�c�q�a�j |

�P�O�r�b�g�̂`�c�ϊ��f�[�^���i�[ |

| �`�c�f�[�^���W�X�^�b�i�`�c�c�q�b�j |

�P�O�r�b�g�̂`�c�ϊ��f�[�^���i�[ |

| �`�c�f�[�^���W�X�^�c�i�`�c�c�q�c�j |

�P�O�r�b�g�̂`�c�ϊ��f�[�^���i�[ |

�Z���N�g�r�b�g�ƃA�i���O���̓`���l���̑Ή�

| �Z���N�g�r�b�g |

�A�i���O���̓`���l�� |

| CK2 |

CK1 |

CK0 |

�P�ꃂ�[�h��

�iSCAN=�O�j |

�X�L�������[�h��

�iSCAN=1) |

| �O |

�O |

�O |

AN0 |

AN0 |

| �O |

�O |

�P |

AN1 |

AN0�`AN1 |

| �O |

�P |

�O |

AN2 |

AN0�`AN�Q |

| �O |

�P |

�P |

AN3 |

AN0�`AN�R |

| �P |

�O |

�O |

AN4 |

AN4 |

| �P |

�O |

�P |

AN5 |

AN�S�`AN�T |

| �P |

�P |

�O |

AN6 |

AN�S�`AN�U |

| �P |

�P |

�P |

AN7 |

AN�S�`AN�V |

6�D�@�⑫

6�D�P�@���d���荞��

�@�g�W�^�R�O�O�@�s�������V���[�Y�ł́A�m�l�h���荞�݈ȊO�ł͑��d���荞�݂͖����B

6�D�Q�@���荞�݂̗D��x

�@�m�l�h�����͑��d���荞�݂��ł���B�h�q�p�O�����ݎ��s���ɁA������D��x�������m�l�h���荞�݂���������ƁA�h�q�p�O�̊��荞�ݏ����͒��f����A�m�l�h���荞�݂����s�����B�@�m�l�h���荞�ݏ������I������Ƃh�q�p�O�̊��荞�݂��ĊJ�����B

�@��ʂ̊��荞�݂ł́A�Q�����̊��荞�݂�����������A�D��x�̍������荞�݂��珈�������B

�@